This page gets you from clone to first successful command quickly, then shows developer-oriented flow and output/report locations.

1. Environment

OpenTestability is developed and tested primarily in WSL/Linux with a Python virtual environment.

Requirements:

- Python 3.8+

- Graphviz (for visualization)

- pip

Example for Ubuntu/WSL:

sudo apt-get update

sudo apt-get install -y python3 python3-venv python3-pip graphviz

2. Install

git clone https://github.com/ranaumarnadeem/OpenTestability.git

cd OpenTestability

python3 -m venv venv

source venv/bin/activate

pip install -r requirements.txt

3. Choose a mode

| Mode | Input model | Use when |

|---|---|---|

--genus |

Verilog, parsed text/json, DAG | You want full command coverage and step-by-step control |

--yosys |

Yosys JSON (or streamlined command set) | You already use Yosys and want short analysis flows |

4. First successful run

Genus mode:

python3 opentest --genus help

python3 opentest --genus cop -i designs/priority_enc.v -j

Yosys mode:

python3 opentest --yosys help

python3 opentest --yosys scoap -i <design.json>

If your run succeeds, outputs are written under project data/result folders and optional reports are created in results/ when verbose mode is enabled.

5. Verbose mode (recommended for debugging)

python3 opentest --genus --verbose cop -i designs/s27.v -j

python3 opentest --yosys --verbose scoap -i <design.json>

Verbose mode generates:

- detailed session logs in

results/log/ - timestamped reports in

results/reports/

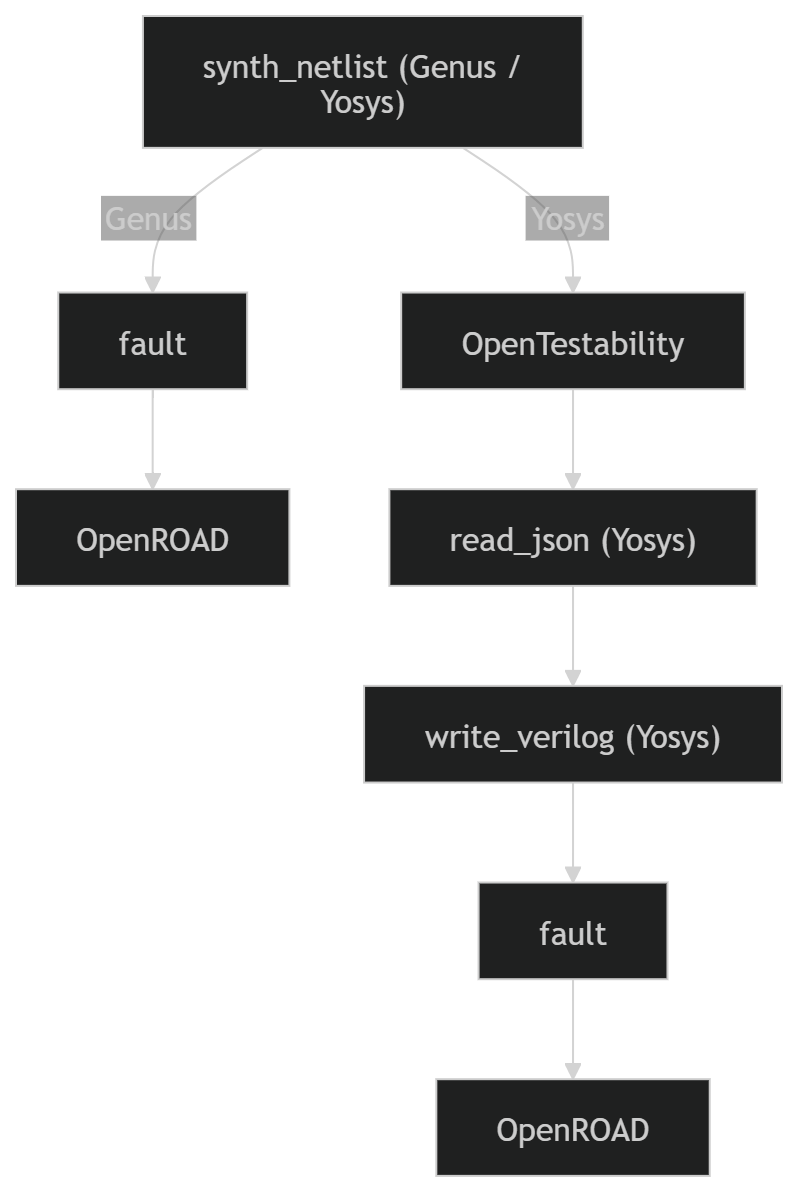

6. DFT Flow

The flow below covers both Genus and Yosys branches:

Typical command sequence (example):

# 1) Analyze and produce metrics

python3 opentest --genus cop -i <synth_netlist.v> -j

# 2) Insert test points and emit enhanced Verilog

python3 opentest --genus tpi -i <netlist.json> -m <metrics.json> -o <design_tp.v> -t 50 -n 10 -v

# 3) Feed generated Verilog to downstream tools

# fault ... <design_tp.v>

# openroad ... <design_tp.v>

7. Yosys mode command example

Example:

# 1) Build Yosys JSON

yosys -p "read_verilog designs/priority_enc.v; synth -top priority_enc; write_json output/priority_enc.json"

# 2) Run OpenTest in Yosys mode

python3 opentest --yosys scoap -i output/priority_enc.json

python3 opentest --yosys analyze_and_add_tp -i output/priority_enc.json --scoap -t 50 -m 10 -v

8. Where reports and outputs are written

results/log/logN.txt: verbose run logs (sequentially numbered)results/log/sessionN.cmd: per-session command historyresults/reports/*: timestamped run reportsdata/results/*: metrics files (COP/SCOAP text/json)data/TPI/*andoutput/*: generated enhanced netlists and flow artifacts

9. Developer quick-start and structure

Developer setup:

source venv/bin/activate

pytest tests/ -v

pytest tests/ -m smoke -v

Top-level structure (developer view):

OpenTestability/

|-- opentest

|-- src/opentestability/

|-- docs/

|-- tests/

| |-- unit/

| |-- integration/

| |-- system/

| `-- fixtures/

|-- data/

|-- results/

`-- output/